|

|

|

|

導電ペースト基板間ビア接続技術 |

|

|

|

OKIグループのプリント配線板(PCB)事業会社であるOKIサーキットテクノロジー(社長:鈴木 正也、本社:山形県鶴岡市、以下OTC)は、このたび、AI半導体に搭載される広帯域メモリーHBM(注1)向けウエハー検査装置用として、従来の124層・板厚7.6mmから約45%高多層化・約2倍高板厚化した180層・板厚15mm PCBの設計・生産技術の開発に成功しました。半導体検査装置用の高多層・高精細・大型PCBに関して、高い設計・生産技術力と実績を有する上越事業所(新潟県上越市)において、2026年10月の量産出荷を目指し、量産技術の確立と設備導入を進めます。 |

|

|

|

|

|

最新のAI半導体では、扱う信号数が膨大であるうえ、プロセスの微細化によりウエハー搭載チップ数も増加しているため、検査装置用PCBには高密度化(狭ピッチ化)と積層数の増加が求められています。一方で、高板厚化に伴い、ビア(注2)の特性インピーダンス(注3)制御の難易度が上がることや、電源層へのビア貫通による電源性能の劣化、細く長いビアを正確に加工するドリル技術の制約などがあり、従来は1枚の超高多層PCBで対応できる上限が124層・板厚7.6mmでした。このため、今後の高速・高周波・高密度のデータ転送ニーズに対応するうえで、従来構造では限界がありました。 |

|

|

|

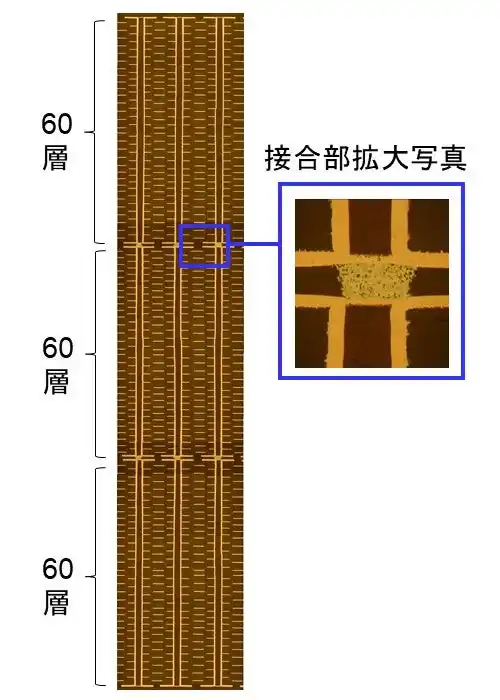

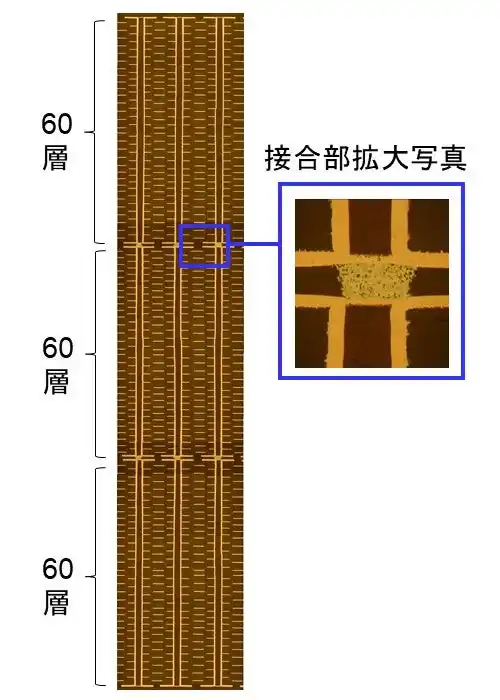

今回OTCでは、複数の多層PCBを積層接続(表面のビアとビアを接続)して超高多層PCBをつくる「導電ペースト基板間ビア接続(Sintering paste for via bonding)技術」と、板厚15mmまで対応可能な「超高厚PCB製造技術」を開発しました。これにより、60層PCBを3枚積層接続して180層・板厚15mmを実現する独自のPCB設計・生産技術を確立しました。多層PCBごとに、従来の確立された技術でビア特性制御、信号品質、電源性能の課題に対応したうえで積層できるため、超高多層化と性能・品質の両立が可能です。新技術により、お客様は将来的なさらなる高速・高周波・高密度データ転送ニーズへの対応が可能になります。 |

|

|

|

OTCは、AI半導体、AIサーバー、宇宙・航空・防衛、次世代通信など、将来的な成長が期待される分野に向けて、今回の技術を開発しました。今後も技術進化に対応し、PCBおよび製造技術のさらなる開発に積極的に取り組んでいきます。 |

|

|

|

なお、OTCは2026年4月28日から5月1日まで米国マサチューセッツ州DCU Convention Centerで開催される「PCB East 2026」OTCブース(No.313)に出展し、本技術を紹介します。 |

|

|

|

|

|

用語解説 |

|

|

|

注1:HBM(High Bandwidth Memory) |

|

次世代広帯域メモリー。複数のDRAMを積層し、専用の高速インターフェースを備える。 |

|

|

|

注2:ビア(VIA HOLE) |

|

多層PCBの層間を電気的に接続する穴。 |

|

|

|

注3:インピーダンス |

|

交流回路での電圧と電流の比をインピーダンスといい、インピーダンスの大きさは、交流回路の電流の流れにくさを表す。インピーダンスが大きいほど回路に流れる電流は小さくなり、インピーダンスが小さいほど回路に流れる電流は大きくなる。 |

|

|

|

|

|

リリース関連リンク |

|

|

|

「導電ペースト基板間ビア接続技術」紹介サイト |

|

|

|

|

|

• |

|

|

• |

|

OKIサーキットテクノロジー株式会社は、通称をOKIサーキットテクノロジーとします。 |

|

|

• |

|

その他、本文に記載されている会社名、商品名は一般に各社の商標または登録商標です。 |

|

|

|

|

|

|